# The HIMALAYAN PHYSICS

A peer-reviewed Journal of Physics

Department of Physics, Prithvi Narayan Campus, Pokhara Nepal Physical Society, Gandaki Chapter, Pokhara

## **Publisher**

Department of Physics, Prithvinarayan Campus, Pokhara Nepal Physical Society, Gandaki Chapter, Pokhara

## The Himalayan Physics

Volume 10, Issue 1, June 2023 ISSN 2542-2545

The Himalayan Physics (HimPhys) is an open access peer-reviewed journal that publishes quality articles which make innovative contributions in all areas of Physics. HimPhys is published annually by Nepal Physical Society (Gandaki Chapter), and Department of Physics, Prithvi Narayan Campus, Pokhara. The goal of this journal is to bring together researchers and practitioners from academia in Nepal and abroad to focus on advanced techniques and explore new avenues in all areas of physical sciences and establishing new collaborations with physics community in Nepal.

## **Chief Editor**

Aabiskar Bhusal

©2023, Publishers. All rights reserved.

This publication is in copyright. Subject to statutory exception and to the provisions of relevant collective licensing agreements, no reproduction of any part may take place without written permission of the publishers.

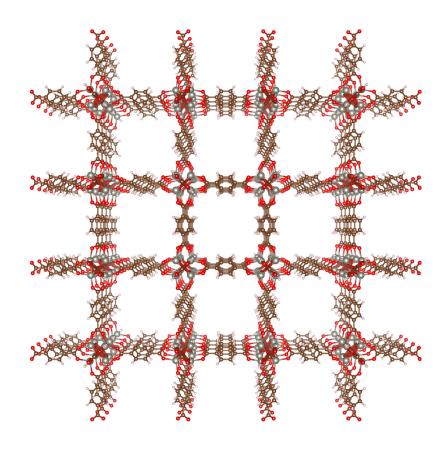

Cover: Ball-and-stick model of MOF-5. © Roshani Sharma. Printed with permission.

# The HIMALAYAN PHYSICS

A peer-reviewed Journal of Physics

**Chief Editor**

Aabiskar Bhusal

# **Publisher**

Department of Physics, Prithvi Narayan Campus, Pokhara Nepal Physical Society, Gandaki Chapter, Pokhara

# Nepal Physical Society

# Gandaki Chapter Pokhara, Nepal

## President

Dr. Krishna Raj Adhikari

## **Immediate Past President**

Min Raj Lamsal

## Vice-President

Dr. Kapil Adhikari

# **Secretary**

Ravi Karki

## **Treasurer**

Dipak Adhikari

# **Joint Secretary**

Amrit Dhakal

# **Editorial Member**

Aabiskar Bhusal

## **Members**

Bhuban Subedi Man Bahadur Roka Sabin Gautam Sristi Gurung Suresh Poudel

# **Advisory Board**

Pabitra Mani Poudyal Surya Bahadur G.C. Parashu Ram Poudel Jeevan Regmi Kul Prasad Dahal

# Himalayan Physics Vol-10(1) (2023)

# TABLE OF CONTENTS

| Adsorption of toxic gases by metal-organic frameworks D. Adhikari, R. Karki, K. Adhikari, N. Pantha                                                                                                       | 1   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Cluster modelling of MOF-5 and its application on gas storage<br>R. Sharma, S. Gurung, K. Adhikari                                                                                                        | 25  |

| Electronic and magnetic properties of ternary sulfide Rb <sub>2</sub> Mn <sub>3</sub> S <sub>4</sub> G.B. Acharya, M.P. Ghimire                                                                           | 33  |

| Dust properties around NGC 7023 nebula in interstellar medium using IRIS, AKARI, and WISE survery  A. Subedi, A. Chaudhary, K. Chaudhary, K. Khatiwada, R. Kandel, S. N. Yadav, D. R. Upadhyay, A. K. Jha | 40  |

| Experimental design for tri-state logic H.S. Mallik, R. Rijal, H.P. Lamichhane                                                                                                                            | 51  |

| Comparison of aerosol optical properties over Lumbini, Pokhara and Langtang-Base Camp S. Sapkota, S. Gautam, A. Gautam, R. Poudel, S. Pokheral, K. Basnet, A. Subedi                                      | 58  |

| Wavelet coherence analysis foF2 over Boulder station during different geomagnetic activity A. Giri, B. Adhikari, B. Shrestha, S. Rimal                                                                    | 66  |

| Complex impedance analysis of soft chemical synthesized NZCF systems D. Parajuli, V.K. Vagolu, K. Chandramoli, N. Murali, B.R. Sharma, N.L. Shah, K. Samatha                                              | 78  |

| Controlling pests in post-harvested wheat using microwave heating H.B. Pariyar, S. Dhungana, D.R. Paudel                                                                                                  | 86  |

| Mean value and velocity variation of ions in different magnetic field at constant obliqueness B.R. Adhikari                                                                                               | 99  |

| Comparative study of solar flux using different empirical models at low land urban industrial zone of Biratnagar Nepal                                                                                    |     |

| F. Limbu, B.R. Tiwari, U. Joshi, J. Regmi, I.B. Karki, K.N. Poudyal                                                                                                                                       | 100 |

\*\*\*\*\*\*

### **Himalayan Physics**

# Experimental design for tri-state logic

Research Article

## Hari Shankar Mallik<sup>1</sup>, Ramesh Rijal<sup>2</sup>, Hari Prasad Lamichhane<sup>1\*</sup>

- 1 Central Department of Physics, Tribhuvan University, Kathmandu, Nepal

- 2 Department of Physics, St. Xavier's College, Kathmandu, Nepal

Abstract: Tri-State Logic device effectively connects many devices into the same data line for data transfer. The Tri-State TTL inverter has three output states such as LOW, HIGH, and open or high-impedance (High-Z) states. The High-Z state either electrically isolates the devices from the data transmission line or connects them one at a time to the data transmission line. The measurement of the floating output (opened or disconnected)

state is a challenging task. This issue can be resolved by introducing a potential divider into the output of the original Tri-State TTL inverter circuit and making it possible for a lab experiment

$\textbf{Keywords:} \ \ \textbf{Data} \ \ \textbf{transmission} \bullet \ \ \textbf{Tri-State} \ \ \textbf{Logic} \bullet \ \ \textbf{High-Z} \bullet \ \ \textbf{TTL} \bullet \ \ \textbf{Inverter}$

## I. Introduction

In digital electronics, data transmission is a prime concern. The data transmission between multiple devices needs switches to be connected and disconnected frequently. If one performs it manually, the system will be slow and unreliable. In this sense, the network will be quite complicated and expensive. On the other hand, the digital data transmission system requires an automatic, fast, reliable, and comparably inexpensive simplified network. To achieve these requirements, a Tri-State Logic system came into existence [1–3], though its name is misleading because it does not use digital logic with three voltage levels [4].

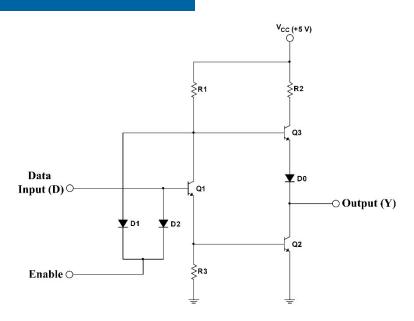

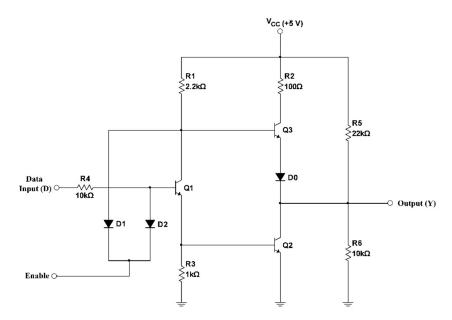

The beauty of the Tri-State Logic gate is that it has an extra logic state called High-Z (high impedance) state in addition to the ordinary digital logic states LOW (0) and High (1). The High-Z state is equivalent to an electrically open (disconnected) state, which makes it possible to share the same line or bus for multiple devices with reliable great speed data transmission [5–7]. Thus, the Tri-State Logic gate became a trademark of National Semiconductor Corporation [4]. The modified TTL (transistor-transistor logic) inverter for Tri-State Logic is shown in Fig. 1 and its corresponding truth table is shown in Table 1 [3, 8]. This modified Tri-State Logic gate is easy to use in the laboratory because of its simplified circuit. However, it is equally difficult to distinguish or realize between the difference between LOW (0) state and a High-Z state because an ordinary voltmeter displays 0 V for both logics.

$<sup>^*</sup>$  Corresponding Author: hari.lamichhanne@cdp.tu.edu.np

Figure 1. Tri-State TTL inverter.

Finally, we have added an extra resistor branch in the output side of the Tri-State Logic gate to remove the ambiguity between the LOW (0) and High-Z states, which enables the modified Tri-State Logic circuit as a lab experiment. The Tri-State TTL inverter circuit, one of many Tri-State devices, is used as a model for explanation purposes in this study.

| Enable | Data Input (D) | Output (Y) |  |

|--------|----------------|------------|--|

| 0      | 0              | Hi-Z       |  |

| O      | 1              | 111-22     |  |

| 1      | 0              | 1          |  |

| 1      | 1              | 0          |  |

Table 1. Truth table for a Tri-Sate TTL inverter

# II. Experimental Design and Working

An experimental circuit of a Tri-State TTL inverter is given in Fig. 2. It is a modified version of the TTL inverter. The two diodes,  $D_1$  and  $D_2$ , are connected in such a way as to enable or disable the data for the output. All transistors are BC547B, all diodes are 1N4007, and all resistors with a 5% tolerance band are used to design the circuits.

### Condition 1: Enable HIGH (1)

When the Enable terminal is at the high-voltage (+5 V), both diodes  $D_1$  and  $D_2$  are effectively not participating in the circuit because both are in reverse biased conditions, and the remaining part of the circuit is

working as a TTL inverter with totem-pole output (R2-Q3-D0-Q2). This totem-pole output stage lowers the output impedance of the gate in the enable condition. In the totem-pole output configuration, both transistors Q2 and Q3 are driven into the cut-off and saturation regions in a complementary manner.

- When the Data input (D) is in the high-voltage (+5 V) state, both transistors Q1 and Q2 are driven into saturation. In this situation, the voltage at the junction of the collector of Q1 and the base of Q3 is nearly equal to 1 V with respect to the ground. The presence of D0 in the circuit ensures the cut-off condition of the transistor Q3 because the available 1 V potential is not sufficient to forward bias two diodes (D0 and the base-to-emitter diode of Q3). The saturated transistor Q2 provides the low-voltage ( $V_{CE(sat)} = \sim 0.2$  V) state for output.

- When the Data input (D) is in the low-voltage (0 V) state, both transistors Q1 and Q2 are driven into

the cut-off region. In this situation, the transistor Q3 is driven into the saturation region as its commonemitter forward short-circuit current gain, β<sub>F</sub>(min) > 26 (since, R1= 2.2 KΩ), and diode D<sub>0</sub> conducts. The

saturated transistor Q3 pulls-up the output at a high-voltage (~3.9 V).

Figure 2. Experimental circuit for Tri-State TTL inverter

### Condition 2: Enable LOW (0)

When the Enable terminal is in the low-voltage (0 V) state, both diodes D1 and D2 pull down the base of transistors Q1 and Q3 to the LOW (0) level no matter what the input voltage-level is. For the silicon diodes the maximum forward bias voltage is 0.7 V. The maximum possible value of 0.7 V input to the base is not sufficient to drive two silicon diodes present in the loops (a)  $V_{BEQ1}$  and  $V_{BEQ2}$ ; (b)  $V_{BEQ3}$  and D0. In this situation, all three transistors Q1, Q2, and Q3 are driven into the cut-off region, and hence the output becomes floating i.e.,

disconnected from both  $V_{\rm CC}$  and the ground. This condition is called a high-impedance (High-Z) output state because no current flows through the output terminal

## III. Results and Discussion

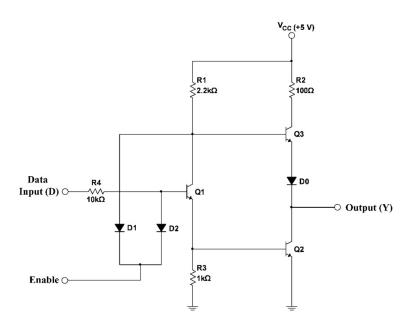

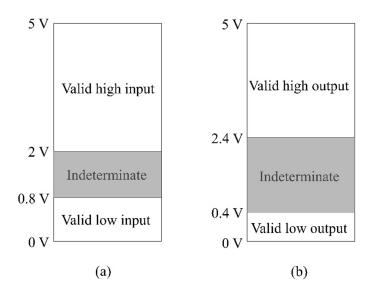

The observations of the experimental circuit given in Fig. 2 are presented in Table 2. All voltages were measured with a digital multimeter having a voltmeter of the least count = 0.01 V. The measured voltages are compared for their states with the TTL input-output profiles, which are shown in Fig. 3.

Figure 3. TTL (a) Input profile (b) Output profile.

When the Enable is HIGH (1) and the Data input (D) is LOW (0), the Output (Y) is in the HIGH (1) state. Also, for the Enable HIGH (1) and Data input (D) HIGH (1) the Output (Y) is observed in the LOW (0) state, which confirms the operation of the regular TTL inverter.

Table 2. Observation table for TTL Tri-State inverter circuit (without potential divider)

| Enable | Data Input        |       | Output            |       |

|--------|-------------------|-------|-------------------|-------|

| Enable | D                 | State | Y                 | State |

| 0.00 V | $0.00~\mathrm{V}$ | 0     | 0.13 V            | 0     |

| 0.00 V | $5.00~\mathrm{V}$ | 1     | $0.11~\mathrm{V}$ | 0     |

| 5.00 V | $0.00~\mathrm{V}$ | 0     | $4.20~\mathrm{V}$ | 1     |

| 5.00 V | $5.00~\mathrm{V}$ | 1     | 0.01 V            | 0     |

Furthermore, in the Enable LOW (0) and the Data input (D) LOW (0) or HIGH (1) the Output (Y) should

be at a High-Z state according to Table 1. However, the observation with this input combination shows a LOW (0) state, which creates confusion between the High-Z state and the LOW (0) state outputs. This confusion is due to the fact that the ordinary voltmeter displays 0 for 0 V measurements as well as for the no current condition (High-Z). Thus, when designing a lab experiment, it is critical to distinguish between the High-Z and LOW (0) states by measurements.

Figure 4. Experimental circuit for Tri-State TTL inverter (with potential divider)

## To distinguish the High-Z and the LOW (0) state:

As far as we know, the TTL Tri-State inverter's Output (Y) terminal cannot source or sink current in the High-Z state. Thus, a potential divider circuit with two resistors R5 (= 22 K $\Omega$ ) and R6 (= 10 K $\Omega$ ) is connected between the V<sub>CC</sub> and the ground terminal of the circuit shown in Fig. 2, and the junction of R5 and R6 is connected to the output (Y), as shown in Fig. 4. Because current sourcing and sinking are not possible at the gate's output terminal under the High-Z state, the V<sub>CC</sub> is simply split between the output potential divider circuit. Additionally, due to the large value (22 K $\Omega$  and 10 K $\Omega$ ) resistors used in this supplementary potential divider circuit, the output impedance of the original circuit will not change in the enable condition.

Further, the observation table for the circuit shown in Fig. 4 is presented in Table 3. In Fig. 4, the Output (Y) is at 1.55 V, when the Enable is LOW (0) and the Data input (D) is either LOW (0) or HIGH (1). This value does not correspond to the LOW (0) or HIGH (1) state of the Output (Y) when compared to Fig. 3. This is for the High-Z state, which is deliberately designed to fall at an indeterminant level of the TTL input-output profile to distinguish it from the HIGH- and LOW-level outputs. This output result is only due to the potential division between resistors R5 and R6. It means there are no sourcing and sinking effects of the transistors Q2 and Q3 to the output which ensures that both transistors Q2 and Q3 are in the cut-off conditions.

Table 3. Observation table for Tri-State TTL inverter circuit (with potential divider)

| Enable | Data              | Data Input |                   | Output |  |  |

|--------|-------------------|------------|-------------------|--------|--|--|

| Епаріе | D                 | State      | Y                 | State  |  |  |

| 0.00 V | 0.00 V            | 0          | 1.55 V            | High-Z |  |  |

|        | $5.00~\mathrm{V}$ | 1          | $1.55~\mathrm{V}$ | High-Z |  |  |

| 5.00 V | 0.00 V            | 0          | 3.93 V            | 1      |  |  |

|        | $5.00~\mathrm{V}$ | 1          | $0.02~\mathrm{V}$ | 0      |  |  |

Now, when the Enable is HIGH (1): (a) Data input (D) is LOW (0) and the Output (Y) is 3.93 V which is in a HIGH (1) state. Here, about 1 V is dropped across R32,  $V_{\text{CEQ3(sat)}}$ , and D0. (b) With the same Enable HIGH (1) and the other input condition i.e. the Data input (D) is HIGH (1), and the Output (Y) goes to the LOW (0) state, which confirms the operation of the regular TTL inverter i.e. the output is the complement of its input.

Hence, the additional potential divider circuit in the output stage does not alter the normal operation of the TTL inverter circuit, also helps to measure the High-Z state and distinguish it from the usual HIGH- and LOW-level data. This small but important approach in the Tri-State TTL inverter makes it possible to study it as an experiment in the electronics laboratory.

## IV. Conclusions

The output of the Tri-State TTL inverter is either in a HIGH, LOW, or High-Z (or electrically disconnected) state corresponding to its Enable and Data input conditions. This High-Z output state of the Tri-State logic device allows sharing the same signal line or bus in the data transmission system without being short-circuited with other connected devices. However, the direct measurement of the voltage of the High-Z output state is misleading in the original Tri-State inverter circuit. The additional potential divider circuit in the output stage of the modified Tri-State inverter circuit is used to distinguish the LOW and High-Z states clearly. This modification allows for designing a Tri-State TTL inverter as a laboratory experiment, which helps to understand how devices can be connected and disconnected automatically in electronics.

Note: In the Large Scale Integration (LSI) system the open collector condition is automatically removed, and the additional resistor circuitry is not necessary.

# V. Acknowledgements

We would like to thank the electronics lab of the Central Department of Physics, Tribhuvan University, Kirtipur, Nepal.

### References

- [1] Pryor RL. Tri-state logic circuit. 1977.

- [2] Garverick TL, Carinalli CP. Active high before open three state integrated circuit output stage. United States Patent; 1985. US Patent 4,529,895.

- [3] Millman J, Grabel A. Microelectronics. 2nd ed. New York: McGraw-Hill; 1987.

- [4] Hill W, Horowitz P. The art of Electronics. 2nd ed. Cambridge University Press; 1997.

- [5] Ay B, Crist S. Design and evaluation of a bipolar tri-state logic family. IEEE Journal of Solid-State Circuits. 1982;17(1):16-9.

- [6] Lancaster DE. TTL cookbook. 1st ed. Indianapolis: H. W. Sams; 1974.

- [7] Crist SC. A tri-state logic family. In: Proceedings of the eighth international symposium on Multiple-valued logic. Washington, DC, USA: IEEE Computer Society Press; 1978. p. 1-6.

- [8] Leach DP, Malvino AP. Digital Principles and Applications. 7th ed. New Delhi: Tatat McGraw-Hill; 2010.