# DESIGN AND IMPLEMENTATION OF VOLTAGE SOURCE INVERTER USING PWM TECHNIQUE

# Saroj Doranga<sup>1</sup>, Rajeev Nepal<sup>2</sup>, Pratigya Timsina<sup>3</sup>

<sup>1</sup> Department of Electronics and Computer Engineering, Thapathali Campus, Institute of Engineering, Kathmandu, Nepal Email: 9846656375saroj@amail.com

<sup>2</sup>Department of Community Medicine, Universal College of Medical Sciences and Teaching Hospital (UCMS-TH) Email: nepalrajeev11@gmail.com

<sup>3</sup>MBS Scholar, Prithvi Narayan Campus, Tribhuvan University, Pokhara, Nepal Correspondence should be addressed to Saroj Doranga Email: pratigyatimsina324@gamil.com

#### **ABSTRACT**

With increasing demand for electricity and diminishing conventional energy resources, there is a pressing need for alternative energy sources. This project aims to construct a Power Inverter that can serve as a reliable power source for heavy equipment. The Voltage Source Inverter (VSI) is a power electronic device that converts DC power to AC power at the required output voltage and frequency level. A two-level inverter produces an output voltage source or current with levels of 0 or positive or negative volts DC. A variable voltage Pulse Width Modulation (PWM) inverter produces a near sinusoidal voltage from several levels of DC voltages, with minimum harmonic distortion and variable output voltage. Using MOSFETs and a microcontroller, this project developed a hardware model for a PWM H-Bridge inverter. A potentiometer serves as a tuner to adjust the duration of the gate signals for driving the MOSFETs, which changes the width of the output voltages, thereby achieving pulse width modulation. PROTEUS simulation models were designed to validate the inverter's performance. The proposed project's objective is to design and implement a Voltage Source Inverter using PWM technique.

Keywords: H-Bridge, MOSFET, PWM, Microcontroller, Voltage Source Inverter, **PROTEUS**

### Introduction

An inverter is an electronic device designed to convert DC power to AC power. The device's input voltage, output voltage, frequency, and power handling capabilities are determined by its circuitry or specific design (Islam & Sharif, 2009). Inverters do not generate power, but rather rely on an external source for their power supply. Power inverters can be purely electronic or include mechanical components. A stable DC source is required to operate a typical inverter circuit that can provide sufficient power for the intended system. Power inverters have higher power, voltage, and current handling capabilities compared to standard inverters (Ismail et al., 2006).

The type of waveform produced by an inverter depends on its circuit design and can include square waves, modified sine waves, pulsed sine waves, pulse-width modulated waves, or sine waves. Modified sine waves and square waves have been the two most commonly commercialized waveform types since 2007. There are two primary methods of producing household plug-in voltage from a lower-voltage DC source, including using a switching boost converter to create higher-voltage DC and then converting it to AC or converting DC to AC at the battery level and using a line-frequency transformer to generate the output voltage (Qazalbash et al., 2009).

The AC output frequency of an inverter is typically 50-60 Hz and can be modified or modulated to a different frequency, making it a variable frequency inverter. Inverter power output is usually expressed in watts or kilowatts and indicates the power available to the device while being driven and indirectly shows the power needed from the DC source (Maiti et al., 2010). The runtime of an inverter powered by batteries is determined by the battery's power capacity and the power being drawn from the inverter at any given time.

In the market for power inverters, there is a wide range of options available with varying degrees of quality, efficiency, and power output capabilities (Sanchez & Canton, 2018). While high-quality and high-efficiency options do exist, they are often quite expensive due to their use of costly, high-power-capable digital components. Pure sine wave inverters are among the high-end options and tend to be expensive (Rashid, M. H. 2009). On the other hand, modified sine wave units can be efficient but may produce a waveform with a high number of harmonics that can be problematic for sensitive equipment like medical monitors (Sethuraman & Waheed, 1988). In contrast, many low-cost inverters produce a square wave or slightly modified square wave with the correct RMS voltage and frequency, but their quality may be questionable (Crowley & Leung, 2011).

Our aim is to offer an affordable and reasonably efficient inverter with a desired waveform output. To achieve this, we will use a combination of PWM and analog components to minimize switching noise and take advantage of the cost savings offered by analog manufacturing techniques.

### Literature Review

In 2014, Yufei Zhou introduced a modulation technique for a modified single-stage boost inverter for grid-connected photovoltaic systems. This system uses a coupled-inductor single-stage boost inverter to boost the voltage of the PV array when it is lower than the grid voltage, and convert DC voltage into AC voltage while feeding current to the grid with a high-power factor and maximum power point tracking (Pop & Dulf, 2004). The technique involves introducing an impedance network with a coupled inductor in front of the three-phase inverter bridge and adjusting the previously forbidden shoot-through zero state to step up the input voltage to a higher voltage level.

In 2005, Carlos Meza and Domingo Biel proposed a solar power generation system that consisted of two power conversion stages: boost DC-DC conversion and buck DC-AC conversion. Their proposed system featured a transformer-less design and included a solar PV array, a boost DC-DC converter, and a full-bridge inverter. The PV array's output voltage was boosted by a step-up chopper and the resulting DC voltage was then inverted using a full-bridge inverter, which functioned as a buck DC-AC converter. The output voltage of the full-wave bridge inverter was square wave AC voltage, and therefore required an L and C filter for conversion to a pure sine voltage (Fernandez et al., 2005). However, due to the two-stage conversion process, the system required more power electronic components, resulting in a larger size, higher cost, and increased switching losses.

In 1998, Zhou and Jovanoic introduced the average current control method to improve the input waveform. This method utilizes a current error amplifier that senses and filters the inductor current. The output of the amplifier drives the PWM modulator (Trigg & Nayar, 2005). The inner current loop helps to minimize the error between the reference and the average input current.

An article authored by David Prince and published in the G.E Review (vol 28, no. 10, p: 676-81) provided a comprehensive overview of the essential components of modern inverters. According to Prince, inverters are electronic devices that convert direct current into single or poly phase alternating current (Qazalbash et al., 2009).

# Methodology

Project involved several methodologies, including surveying power inverter manufacturers to gather information on their construction procedures and analyzed the specifications of currently available power inverters to identify

potential design improvements or cost reductions (Aziz, & Salam, 2003). We also conducted a literature review to expand our knowledge of inverter circuit modules, their operation, and common issues (Dimitriu et al., 2003). After identifying components and finalizing the circuit design, we simulated the inverter circuit in PROTEUS to test its functionality and arrange the output properly (Nanda & Sengupta, 2018). The circuit was then tested and debugged to ensure it operates as planned. Throughout the project, documentation is done with progress and findings, including the full circuit diagram, its operation, advantages, limitations, feasibility, reliability, and other important aspects of the project.

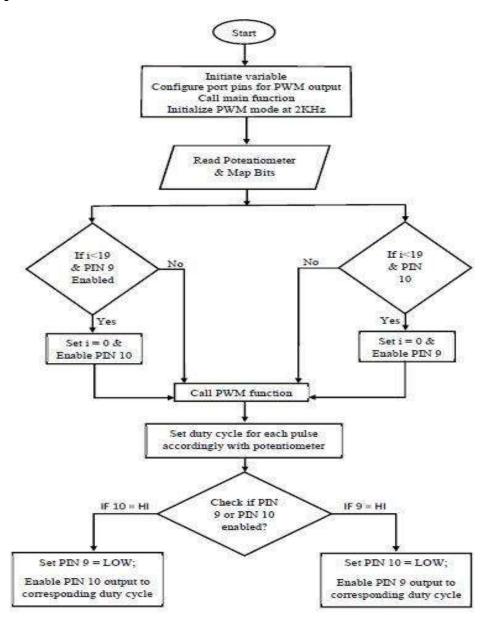

### **Flowchart**

# Algorithm: PWM output control

Step 1: Start.

Step 2: Initialize variables and configure port pins for PWM output.

Step 3: Call the main function.

Step 4: Initialize PWM mode to operate at a frequency of 2 KHz.

Step 5: Read the value of the potentiometer and map its bits.

Step 6: Check if the value of i is less than 19 and if PIN 9 is enabled.

If yes, set i to 0 and enable PIN 10.

If no, call the PWM function.

Step 7: Check if the value of i is less than 19 and if PIN 10 is enabled.

If yes, set i to 0 and enable PIN 9.

If no, call the PWM function.

Step 8: Set the duty cycle for each pulse according to the value of the potentiometer.

Step 9: Check if PIN 9 or PIN 10 is enabled.

If PIN 9 is high, set PIN 10 to low and enable PIN 9 to the corresponding duty cycle.

If PIN 10 is high, set PIN 9 to low and enable PIN 10 to the corresponding duty cycle.

Step 10: Display the corresponding voltage value.

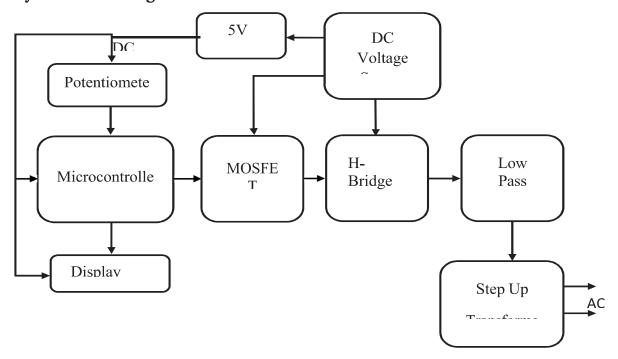

# System block diagram

Fig 1: System block diagram

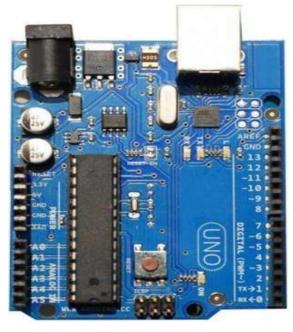

The algorithm provided is a set of steps for creating an inverter using a potentiometer, microcontroller, MOSFET driver, H-bridge MOSFET, low pass filter, step-up transformer, DC source, display unit, and DC regulator (Nanda, & Sengupta, 2018). The potentiometer is a resistor with a sliding or rotating contact that serves as an adjustable voltage divider, allowing the desired voltage to be obtained by rotating the potentiometer in a clockwise or counterclockwise direction (Roy, S, 2007). The microcontroller, in this case, an Arduino, is used to achieve the desired programming needs and MOSFET switching or driving (Dewan, & Agu, 1983). The MOSFET driver is necessary because the MOSFET used for PWM needs to be switched rapidly and completely.

The H-bridge MOSFET serves as electrical switches to deliver DC at one polarity for one half-cycle and then the opposite polarity for the other half-cycle, generating an AC waveform (Krein, P. T, 1998). A low pass filter is used to obtain a smoother signal output, and a step-up transformer is used to increase the magnitude of the output AC voltage to be used on demanding loads (Dawson & Jain, 1991). A display unit, such as an LCD, is interfaced to monitor the tuned voltage values, providing greater precision than tuning a potentiometer alone. Lastly, a 5V regulator is used to provide constant DC power from a 12V battery, as some modules require a constant DC supply for operation (Roy & Sengupta , 2012).

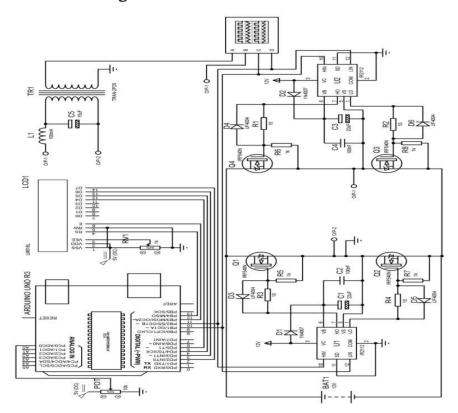

# Simulated circuit diagram

The simulation of a single phase voltage source inverter on Proteus is shown in the circuit arrangement. The full bridge (H-bridge) configuration of four MOSFETs produces alternating output, with each set of MOSFET operating for a determined time based on the required frequency output. In order to conduct, MOSFET requires a gate pulse generated by Arduino UNO R3 which supplies IR2112 driver for efficient driving of Bridge MOSFET. PWM technique is employed to obtain a smooth voltage waveform. Phase correct PWM at a frequency of 2000 Hz is chosen to generate a smooth PWM signal using Arduino. With a frequency of 50Hz, the time period is 20ms, and 10ms is the half cycle period (Mendes et al., 2014). The frequency of 2000Hz implies that each pulse's period is 500us, with 20 pulses for each half cycle. The duty cycles of each pulse are defined with the aid of a sine lookup table (sine array). A 10K potentiometer connected to the Arduino's analog pin changes the duty cycle of each pulse, causing a corresponding change in the output voltage of the inverter.

# Implementation of the hardware

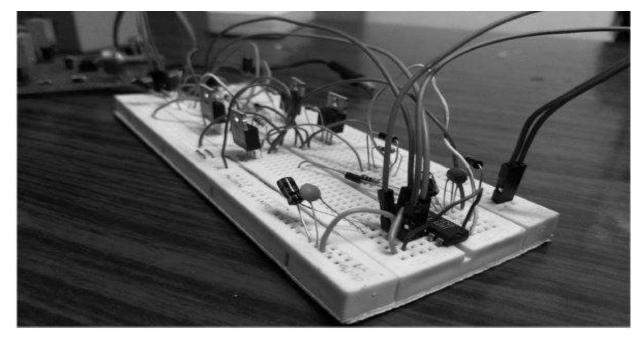

Initially, the circuit was connected on a breadboard and both the circuit diagram and its corresponding output waveforms are depicted in the figure below.

Fig 2: Inverter Circuit on Breadboard

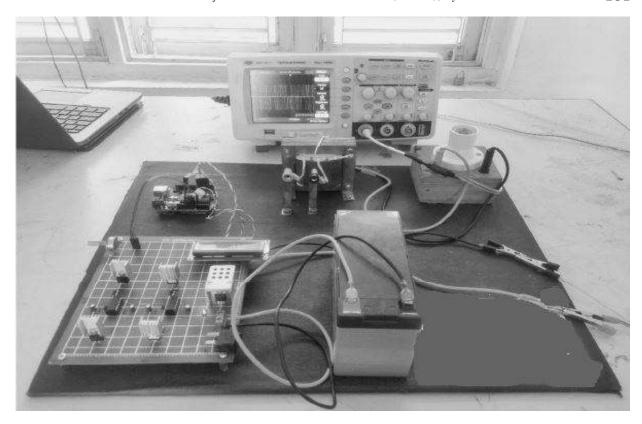

The full bridge configuration was set up with four MOSFETs and the components were arranged according to the simulated circuit in PROTEUS. The resulting output signal was observed on an oscilloscope, and the obtained signal was an unfiltered AC signal, as depicted in the figure below.

Fig 3: H-Bridge inverter

# **Results and Discussion**

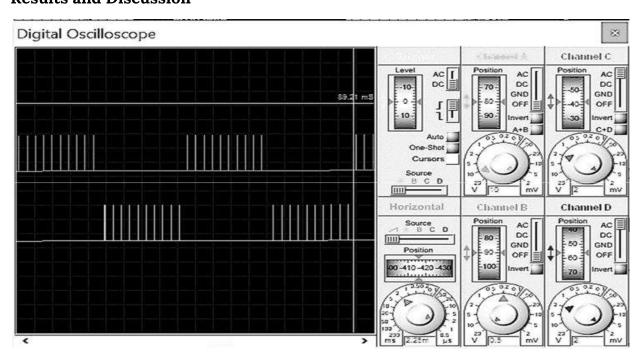

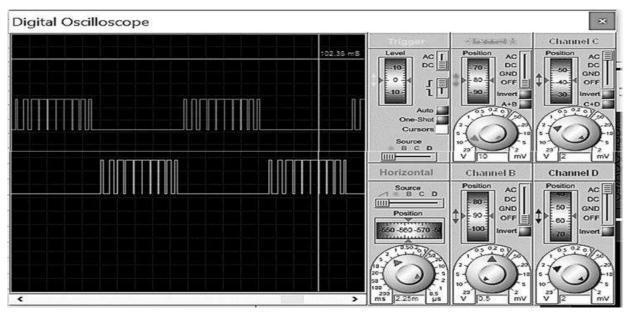

Fig 4: Signal at 1% POT value

The figure above shows the output signal obtained from tuning the potentiometer to 1% of its value. It is clearly visible that the width of the signal is at its minimum.

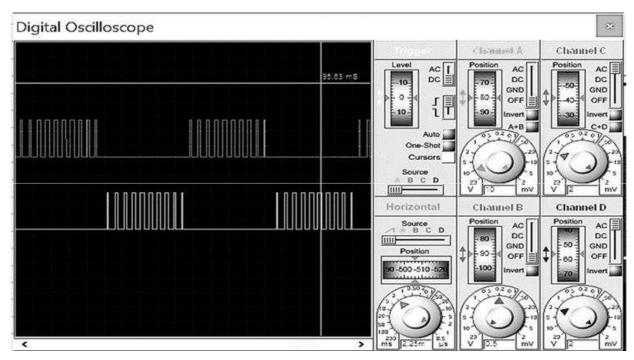

Fig 5: Signal at 6% POT value

The signal obtained from tuning the potentiometer to 6% of the POT value can be observed. Similarly, when the potentiometer is tuned to 50% of the POT value, observation can be done with the signal's width varying and increasing in accordance with the varying POT value.

Fig 6: Signal at 50% POT value

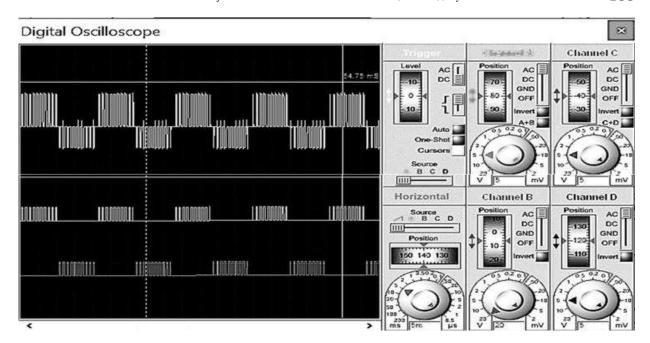

Fig 7: Unfiltered AC signal

The above figure illustrates the raw AC waveform obtained from the H-Bridge MOSFET, after the MOSFET Bridge was supplied with signals generated from the Arduino.

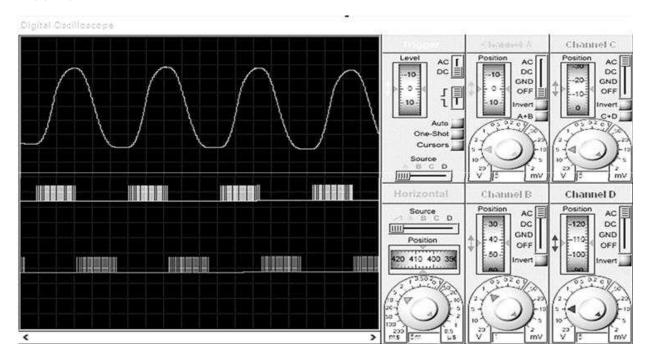

Fig 8: Output sine wave

After passing through the H-Bridge MOSFET, the output waveform was filtered using a LC filter, resulting in the waveform shown above. The most challenging

aspect was producing a pure sine wave from the filter, but with appropriate values of L and C, a modified sine wave of such nature is achieved.

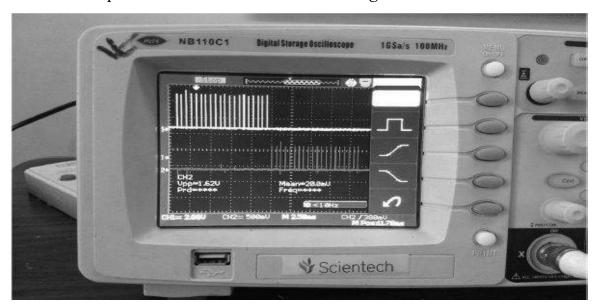

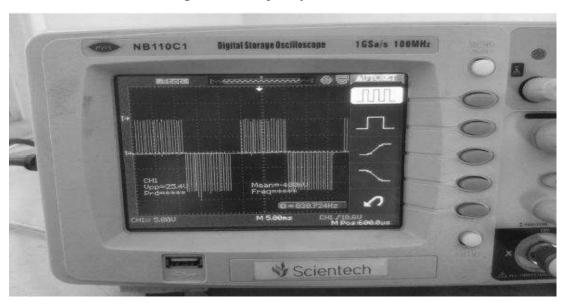

Once the circuit was constructed on the breadboard, it was then fabricated onto the kit board. The output signal from the circuit was analyzed using an oscilloscope and the resulting waveforms are illustrated. The gate signal for two pair MOSFET was generated using Arduino and fed to the oscilloscope. The observed output waveform can be seen in the figure below.

Fig 9: Gate signal for MOSFET

Fig 10: Unfiltered AC output

From the output of the circuit after assembling all the components on the PCB board the unfiltered AC signal was obtained as shown in figure 9.

### Conclusion

Based on our findings, we affirm that Voltage Source Inverter is a highly promising technology in the power system industry with numerous applications and advantages due to its controlled variable output feature. We simulated the inverter circuit using an H-Bridge MOSFET arrangement in PROTEUS simulation program and achieved an acceptable modified sine wave output that was further smoothed using an LC Filter configuration to remove most of the distortion on the signal and produce a proper sine AC signal.

The desired amplitude of the output AC signal was obtained by adjusting the potentiometer, which changed the width of the gate pulse to drive the MOSFET and alter the amplitude of the AC signal. We have completed the design and testing of a single-phase voltage source inverter, with a detailed description of all the components used in the fabrication of the inverter.

### References

- Aziz, J., & Salam, Z. (2003). An alternative PWM scheme for multilevel voltage source inverter. National Power Engineering Conference (pp. 83-87).

- Crowley, I. F., & Leung, H. F. (2011). PWM Techniques: A Pure Sine Wave Inverter. Worcester Polytechnic Institute.

- Dawson, F. P., & Jain, P. (1991). A comparison of load commutated inverter systems for induction heating and melting applications. *Transactions on Power Electronics*, 6(3), 430-441.

- Dewan, S., & Agu, M. (1983). The load-independent commutated voltage source inverter for induction heating. *Transactions on Magnetics*, 19(5), 2079–2081.

- Dimitriu, L., Lucanu, M., Aghion, C., & Ursaru, O. (2003). Control with microcontroller for PWM single-phase inverter. *In Signals, Circuits and Systems* (Vol. 1, pp. 265-268).

- Fernandez, A., Sebastian, J., Hernando, M., & Rodriguez, J. (2005). Design tips for a general purpose application PWM inverter based on a low cost microcontroller. In 2005 IEEE 36th Power Electronics Specialists Conference (pp. 786-791).

- Islam, S. M., & Sharif, G. M. (2009). Microcontroller based sinusoidal PWM inverter for photovoltaic application. *International Conference on the Developments in Renewable Energy Technology* (pp. 1-4).

- Ismail, B., Taib, S., Saad, A. M., Isa, M., & Hadzer, C. M. (2006). Development of a SPWM microcontroller-based inverter. phase In 2006 IEEE International Power and Energy Conference (pp. 437-440).

- Krein, P. T. (1998). Elements of power electronics.

- Maiti, A., Choudhuri, S., Bera, J., Banerjee, T., & Maitra, S. (2010). Development of microcontroller based single phase SPWM inverter with remote control facility. Joint International Conference on Power Electronics, Drives and Energy Systems (pp. 1-5).

- Mendes Duarte, R., & Klaric Felic, G. (2014). Analysis of the coupling coefficient in inductive energy transfer systems. Active and Passive Electronic Components, 2014.

- Nanda, A., Kar, A., & Sengupta, M. (2018). Design, Analysis, Simulation, Fabrication and Experiments on a Voltage Source Inverter Fed Induction Heating Prototype. International Conference on Power Electronics, Drives and Energy Systems (pp. 1-6).

- Pop, O., Chindris, G., & Dulf, A. (2004). Using DSP technology for true sine PWM generators for power inverters. International Spring Seminar on Electronics Technology: Meeting the Challenges of Electronics Technology Progress (Vol. 1, pp. 141-146).

- Qazalbash, A. A., Amin, A., Manan, A., & Khalid, M. (2009, March). Design and implementation of microcontroller based PWM technique for sine wave inverter. International Conference on Power Engineering, Energy and Electrical Drives (pp. 163-167).

- Rashid, M. H. (2009). Power electronics: circuits, devices, and applications. Pearson Education India.

- Roy, M., & Sengupta, M. (2012). Design, fabrication and testing of two different laboratory prototypes of CSI-based induction heating units. Journal of the Institution of Engineers. 93, 133-141.

- Roy, S. (2007). Finite element based design, fabrication and tasting of fed single phase induction furnace for application in bar/billet heating. Billet Heating.

- Sanchez, J., & Canton, M. P. (2018). Microcontroller programming: the microchip PIC. CRC Press.

- Sethuraman, S. K., & Waheed, M. A. (1988). A single-chip microcontroller based real-time PWM inverter. *International Conference on Power Electronics and Variable-Speed Drives* (pp. 390-393).

- Trigg, M. C., Dehbonei, H., & Nayar, C. V. (2005). Digital sinusoidal PWM generation using a low-cost micro-controller based single-phase inverter. Conference on Emerging Technologies and Factory Automation (Vol. 1, pp. 4-pp).

## APPENDIX-I

```

#include <LiquidCrystal.h>

LiquidCrystal lcd(7,6, 5, 4, 3, 2);

int sine[]={78,155,227,294,354,405,446,476,494,500},

500,494,476,446,405,354,294,227,155,78};

float Ton = 0.0;

float Toff = 0.0;

float potval;

void setup() {

Serial.begin(9600);

pinMode(9, OUTPUT);

pinMode(10, OUTPUT);

lcd.begin(16, 2);

lcd.print("Voltage:");

lcd.setCursor(7, 2);

lcd.print("volts");

void loop() {

float value = analogRead(A0);

potval = map(value, 0, 1023, 0, 100);

Serial.println(potval);

float voltage = (value/1023)*9;

// Print a message to the LCD.

lcd.setCursor(0, 1);

lcd.print(voltage);

digitalWrite(10, LOW);

for(int i=0;i<=19;i++)

int x = sine[i];

Ton = x*potval/100;

Toff = 500-Ton;

digitalWrite(9, HIGH);

delayMicroseconds(Ton);

digitalWrite(9, LOW);

delayMicroseconds(Toff);

digitalWrite(9, LOW);

for(int i=0;i<=19;i++)

int x = sine[i];

Ton = x*potval/100;

Toff = 500-Ton;

```

```

digitalWrite(10, HIGH);

delayMicroseconds(Ton);

digitalWrite(10, LOW);

delayMicroseconds(Toff);

}

}

```

### APPENDIX-II

# Arduino UNO R3:

Microcontroller: ATmega328

Operating Voltage: 5V

Input Voltage (recommended): 7-12V

Input Voltage (limits): 6-20V

Digital I/O Pins: 14 (of which 6 provide PWM output)

Analog Input Pins: 6

DC Current per I/O Pin: 40 mA DC Current for 3.3V Pin: 50 mA

Flash Memory: 32 KB (ATmega328) of which 0.5 KB used by bootloader

SRAM: 2 KB (ATmega328) EEPROM: 1 KB (ATmega328)

Clock Speed: 16 MHz

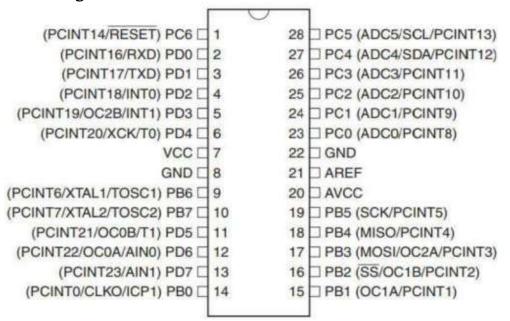

# Pin Configuration:

### APPENDIX-III

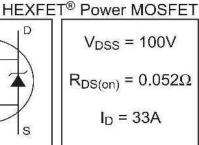

# International TOR Rectifier

PD-91341A

# IRF540N

- Advanced Process Technology

- Dynamic dv/dt Rating

- 175°C Operating

- Fast Switching

- Fully Avalanche Rated

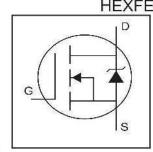

## Description

Fifth Generation HEXFETs from International Rectifier utilize advanced processing techniques to achieve extremely low on-resistance per silicon area. This benefit, combined with the fast switching speed and ruggedized device design that HEXFET Power MOSFETs are well known for, provides the designer with an extremely efficient and reliable device for use in a wide variety of applications.

The TO-220 package is universally preferred for all commercial-industrial applications at power dissipation levels to approximately 50 watts. The low thermal resistance and low package cost of the TO-220 contribute to its wide acceptance throughout the industry.

# **Absolute Maximum Ratings**

|                                         | Parameter                                       | Max.                   | Units |

|-----------------------------------------|-------------------------------------------------|------------------------|-------|

| I <sub>D</sub> @ T <sub>C</sub> = 25°C  | Continuous Drain Current, V <sub>GS</sub> @ 10V | 33                     |       |

| I <sub>D</sub> @ T <sub>C</sub> = 100°C | Continuous Drain Current, V <sub>GS</sub> @ 10V | 23                     | A     |

| I <sub>DM</sub>                         | Pulsed Drain Current ①                          | 110                    |       |

| P <sub>D</sub> @T <sub>C</sub> = 25°C   | Power Dissipation                               | 140                    | W     |

|                                         | Linear Derating Factor                          | 0.91                   | W/°C  |

| V <sub>GS</sub>                         | Gate-to-Source Voltage                          | ± 20                   | V     |

| E <sub>AS</sub>                         | Single Pulse Avalanche Energy@                  | 300                    | mJ    |

| I <sub>AR</sub>                         | Avalanche Current①                              | 16                     | A     |

| E <sub>AR</sub>                         | Repetitive Avalanche Energy®                    | 14                     | mJ    |

| dv/dt                                   | Peak Diode Recovery dv/dt ③                     | 5.0                    | V/ns  |

| Tj                                      | Operating Junction and                          | -55 to + 175           |       |

| T <sub>STG</sub>                        | Storage Temperature Range                       |                        | °C    |

|                                         | Soldering Temperature, for 10 seconds           | 300 (1.6mm from case ) |       |

|                                         | Mounting torque, 6-32 or M3 srew                | 10 lbf•in (1.1N•m)     | *     |

### **Thermal Resistance**

|                  | Parameter                           | Тур. | Max. | Units |

|------------------|-------------------------------------|------|------|-------|

| R <sub>eJC</sub> | Junction-to-Case                    | 3-3  | 1.1  |       |

| R <sub>0CS</sub> | Case-to-Sink, Flat, Greased Surface | 0.50 | 5-3  | °C/W  |

| $R_{\theta JA}$  | Junction-to-Ambient                 | S    | 62   |       |

# IRF540N

# Electrical Characteristics @ T<sub>J</sub> = 25°C (unless otherwise specified)

|                                        | Parameter                            | Min.            | Тур.    | Max.         | Units | Conditions                                                          |

|----------------------------------------|--------------------------------------|-----------------|---------|--------------|-------|---------------------------------------------------------------------|

| V <sub>(BR)DSS</sub>                   | Drain-to-Source Breakdown Voltage    | 100             | 5 5     | 10 TI        | ٧     | $V_{GS} = 0V, I_D = 250\mu A$                                       |

| ΔV <sub>(BR)DSS</sub> /ΔT <sub>J</sub> | Breakdown Voltage Temp. Coefficient  | B 18            | 0.11    | -            | V/°C  | Reference to 25°C, I <sub>D</sub> = 1mA                             |

| R <sub>DS(on)</sub>                    | Static Drain-to-Source On-Resistance | # #             | 15 (8)  | 0.052        | Ω     | V <sub>GS</sub> = 10V, I <sub>D</sub> = 16A ⊕                       |

| V <sub>GS(th)</sub>                    | Gate Threshold Voltage               | 2.0             |         | 4.0          | ٧     | $V_{DS} = V_{GS}, I_{D} = 250 \mu A$                                |

| g <sub>fs</sub>                        | Forward Transconductance             | 11              | 22. 134 | 22 W.        | S     | V <sub>DS</sub> = 50V, I <sub>D</sub> = 16A                         |

| L                                      | Drain-to-Source Leakage Current      | (Ve - 16)       | Z 78    | 25           | μA    | V <sub>DS</sub> = 100V, V <sub>GS</sub> = 0V                        |

| loss                                   | Drain-to-Source Leakage Current      | 24              | (C) 10  | 250          | μА    | V <sub>DS</sub> = 80V, V <sub>GS</sub> = 0V, T <sub>J</sub> = 150°C |

| D.                                     | Gate-to-Source Forward Leakage       | 7/4 - 15°       | e: 3    | 100          | nA    | V <sub>GS</sub> = 20V                                               |

| IGSS                                   | Gate-to-Source Reverse Leakage       | - V             |         | -100         | ПА    | V <sub>GS</sub> = -20V                                              |

| Qg                                     | Total Gate Charge                    | 7537            | SE 12   | 94           |       | I <sub>D</sub> = 16A                                                |

| Qgs                                    | Gate-to-Source Charge                | 19—30           | 2516    | 15           | nC    | $V_{DS} = 80V$                                                      |

| Q <sub>gd</sub>                        | Gate-to-Drain ("Miller") Charge      | (4 <u>—</u> 8)  | 151 LG  | 43           |       | V <sub>GS</sub> = 10V, See Fig. 6 and 13 <sup>(4)</sup>             |

| t <sub>d(on)</sub>                     | Turn-On Delay Time                   | 11—17           | 8.2     | E E          | 8     | V <sub>DD</sub> = 50V                                               |

| t <sub>r</sub>                         | Rise Time                            | 1-1             | 39      | 223          | ns    | I <sub>D</sub> = 16A                                                |

| $t_{d(off)}$                           | Turn-Off Delay Time                  | 11—17           | 44      | 21           | ns    | $R_G = 5.1\Omega$                                                   |

| t <sub>f</sub>                         | Fall Time                            | 1-1             | 33      | 0.00         |       | $R_D = 3.0\Omega$ , See Fig. 10 ①                                   |

| L <sub>D</sub>                         | Internal Drain Inductance            |                 | 4.5     | -            | 244   | Between lead,<br>6mm (0.25in.)                                      |

| Ls                                     | Internal Source Inductance           | 2_3             | 7.5     | 0 <u> </u> 0 |       | and center of die contact                                           |

| Ciss                                   | Input Capacitance                    | 3 <del></del> 3 | 1400    | -            |       | $V_{GS} = 0V$                                                       |

| Coss                                   | Output Capacitance                   |                 | 330     | _            | pF    | $V_{DS} = 25V$                                                      |

| Crss                                   | Reverse Transfer Capacitance         |                 | 170     |              |       | f = 1.0MHz, See Fig. 5                                              |

# **Source-Drain Ratings and Characteristics**

|                 | Parameter                                 | Min.       | Тур.     | Max.     | Units    | Conditions                                                          |

|-----------------|-------------------------------------------|------------|----------|----------|----------|---------------------------------------------------------------------|

| Is              | Continuous Source Current<br>(Body Diode) | 19——(1)    | _        | 33       | A        | MOSFET symbol showing the                                           |

| Ism             | Pulsed Source Current<br>(Body Diode) ①⑤  | 19         | -        | 110      |          | integral reverse p-n junction diode.                                |

| V <sub>SD</sub> | Diode Forward Voltage                     | 987 10     |          | 1.3      | ٧        | T <sub>J</sub> = 25°C, I <sub>S</sub> = 16A, V <sub>GS</sub> = 0V @ |

| t <sub>rr</sub> | Reverse Recovery Time                     | NE20       | 170      | 250      | ns       | T <sub>J</sub> = 25°C, I <sub>F</sub> = 16A                         |

| Qrr             | Reverse RecoveryCharge                    | ( <u>-</u> | 1.1      | 1.6      | μC       | di/dt = 100A/µs ∅                                                   |

| ton             | Forward Turn-On Time                      | Intr       | insic tu | rn-on ti | me is ne | egligible (turn-on is dominated by L <sub>S</sub> +L <sub>I</sub>   |

#### Notes:

- ① Repetitive rating; pulse width limited by max. junction temperature. ( See fig. 11 )

- ② Starting  $T_J = 25$ °C, L = 2.0mH  $R_G = 25\Omega$ ,  $I_{AS} = 16A$ . (See Figure 12)

- $\ \Im \ I_{SD} \leq 16A, \ di/dt \leq 210A/\mu s, \ V_{DD} \leq V_{(BR)DSS}, \ T_{J} \leq 175^{\circ}C$

- ④ Pulse width ≤ 300µs; duty cycle ≤ 2%

APPENDIX-IV

# International TOR Rectifier

Data Sheet No. PD60026-R

ISSN: 3021-9108

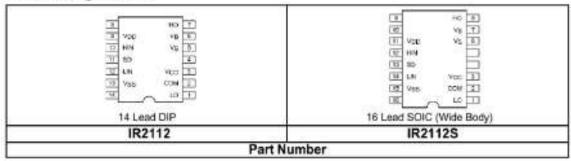

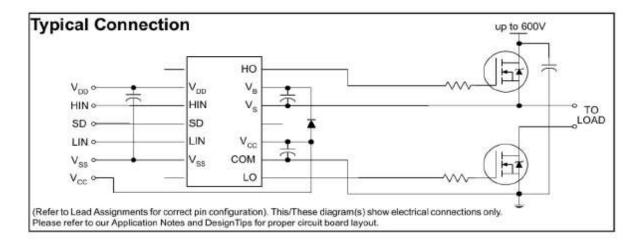

IR2112(S) & (PbF)

# HIGH AND LOW SIDE DRIVER

## **Features**

- · Floating channel designed for bootstrap operation

- Fully operational to +600V

- Tolerant to negative transient voltage dV/dt immune

- Gate drive supply range from 10 to 20V

- · Undervoltage lockout for both channels

- 3.3V logic compatible

Separate logic supply range from 3.3V to 20V

Logic and power ground £V offset

- · CMOS Schmitt-triggered inputs with pull-down

- · Cycle by cycle edge-triggered shutdown logic

- · Matched propagation delay for both channels

- · Outputs in phase with inputs

- Also available LEAD-FREE

# Description

The IR2112(S) is a high voltage, high speed power MOSFET and IGBT driver with independent high and low side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. Logic inputs are compatible with standard CMOS or LSTTL outputs, down

# **Product Summary**

| Voffset            | 600V max.       |

|--------------------|-----------------|

| I <sub>O</sub> +/- | 200 mA / 420 mA |

| Vout               | 10 - 20V        |

| ton/off (typ.)     | 125 & 105 ns    |

| Delay Matching     | 30 ns           |

# Packages 4 8 1

to 3.3V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver crossconduction. Propagation delays are matched to simplify use in high frequency applications. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high side configuration which operates up to 600 volts.

# IR2112(S)&(PbF)

# Absolute Maximum Ratings

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The Thermal Resistance and Power Dissipation ratings are measured under board mounted and still air conditions. Additional information is shown in Figures 28 through 35.

| Symbol              | Definition                                         |                | Min.                  | Max.                  | Units  |

|---------------------|----------------------------------------------------|----------------|-----------------------|-----------------------|--------|

| VB                  | High Side Floating Supply Voltage                  |                | -0.3                  | 625                   |        |

| ٧s                  | High Side Floating Supply Offset Voltage           |                | V <sub>B</sub> - 25   | V <sub>B</sub> + 0.3  |        |

| VHO                 | High Side Floating Output Voltage                  |                | V <sub>S</sub> - 0.3  | V <sub>B</sub> + 0.3  | ì      |

| Vcc                 | Low Side Fixed Supply Voltage                      |                | -0.3                  | 25                    | ٧      |

| VLO                 | Low Side Output Voltage                            |                | -0.3                  | V <sub>CC</sub> + 0.3 | 0.80   |

| Voo                 | Logic Supply Voltage                               |                | -0.3                  | V <sub>SS</sub> + 25  |        |

| Vss                 | Logic Supply Offset Voltage                        |                | Vcc - 25              | Vcc+0.3               |        |

| VIN                 | Logic Input Voltage (HIN, LIN & SD)                |                | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 |        |

| dV <sub>s</sub> /dt | Allowable Offset Supply Voltage Transient (        | Figure 2)      | -                     | 50                    | V/ns   |

| PD                  | Package Power Dissipation @ T <sub>A</sub> ≤ +25°C | (14 Lead DIP)  |                       | 1.6                   | w      |

|                     |                                                    | (16 Lead SOIC) | 122                   | 1,25                  | **     |

| RTHIA               | Thermal Resistance, Junction to Ambient            | (14 Lead DIP)  | -                     | 75                    | TETRAL |

|                     | (16 Lead SOIC)                                     |                | -                     | 100                   | -C/W   |

| Tj                  | Junction Temperature                               |                | -                     | 150                   |        |

| Ts                  | Storage Temperature                                |                | -55                   | 150                   | °C     |

| TL                  | Lead Temperature (Soldering, 10 seconds)           | ()             | -                     | 300                   |        |

# Recommended Operating Conditions

The Input/Output logic timing diagram is shown in Figure 1. For proper operation the device should be used within the recommended conditions. The VS and VSS offset ratings are tested with all supplies biased at 15V differential. Typical ratings at other bias conditions are shown in Figures 36 and 37.

| Symbol          | Definition                                 | Min.                | Max.                 | Units |

|-----------------|--------------------------------------------|---------------------|----------------------|-------|

| VB              | High Side Floating Supply Absolute Voltage | V <sub>S</sub> + 10 | V <sub>8</sub> + 20  |       |

| ٧s              | High Side Floating Supply Offset Voltage   | Note 1              | 600                  |       |

| VHO             | High Side Floating Output Voltage          | Vs                  | Va                   |       |

| Vcc             | Low Side Fixed Supply Voltage              | 10                  | 20                   | 1000  |

| VLO             | Low Side Output Voltage                    | 0                   | Vcc                  | ν     |

| V <sub>DO</sub> | Logic Supply Voltage                       | Vss + 3             | V <sub>SS</sub> + 20 |       |

| Vss             | Logic Supply Offset Voltage                | -5 (Note 2)         | 5                    |       |

| V <sub>IN</sub> | Logic Input Voltage (HIN, LIN & SD)        | V <sub>SS</sub>     | Vpp                  |       |

| TA              | Ambient Temperature                        | -40                 | 125                  | "C    |

Note 1: Logic operational for V<sub>S</sub> of -5 to +600V. Logic state held for V<sub>S</sub> of -5V to -V<sub>BS</sub>. (Please refer to the Design Tip DT97-3 for more details).

Note 2: When Voo < 5V, the minimum Vss offset is limited to -Voo.

# IR2112(S) & (PbF)

# **Dynamic Electrical Characteristics**

VBIAS (VCC, VBS, VDD) = 15V, CL = 1000 pF, TA = 25°C and VSS = COM unless otherwise specified. The dynamic electrical characteristics are measured using the test circuit shown in Figure 3.

| Symbol | Definition                          | Figure | Min. | Тур. | Max. | Units | <b>Test Conditions</b> |

|--------|-------------------------------------|--------|------|------|------|-------|------------------------|

| ton    | Turn-On Propagation Delay           | 7      | -    | 125  | 180  |       | V <sub>S</sub> = 0V    |

| tott   | Turn-Off Propagation Delay          | 8      |      | 105  | 160  |       | Vs = 600V              |

| lad    | Shutdown Propagation Delay          | 9      |      | 105  | 160  | ns    | Vs = 600V              |

| tr     | Turn-On Rise Time                   | 10     | -    | 80   | 130  |       | 1,                     |

| le le  | Turn-Off Fall Time                  | 11     |      | 40   | 65   |       |                        |

| MT     | Delay Matching, HS & LS Turn-On/Off |        | -    | -    | 30   |       |                        |

# Static Electrical Characteristics

$V_{BUNS}$  ( $V_{CU}$ ,  $V_{BS}$ ,  $V_{DU}$ ) = 15V,  $T_N$  = 25°O and  $V_{SS}$  = COM unless otherwise specified. The  $V_{IN}$ ,  $V_{IH}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$  and are applicable to all three logic input leads: HIN, LIN and SD. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads: HO or LO.

| Symbol | Definition                                                      | Figure | Min. | Тур. | Max. | Units | <b>Test Conditions</b>                                               |

|--------|-----------------------------------------------------------------|--------|------|------|------|-------|----------------------------------------------------------------------|

| ViH    | Logic "1" Input Voltage                                         | 12     | 9.5  | -    | -    | 1     |                                                                      |

| VIL    | Logic "0" Input Voltage                                         | 13     |      | -    | 6.0  | V     |                                                                      |

| VoH    | High Level Output Voltage, VBIAS - VO                           | 14     | -    | _    | 100  | 1000  | IO = 0A                                                              |

| Vol    | Low Level Output Voltage, Vo                                    | 15     | -    | -    | 100  | mV    | I <sub>O</sub> = 0A                                                  |

| ILK    | Offset Supply Leakage Current                                   | 16     | -    | -    | 50   |       | $V_{\rm B} = V_{\rm S} = 600V$                                       |

| lass   | Quiescent V <sub>BS</sub> Supply Current                        | 17     | -    | 25   | 60   |       | V <sub>IN</sub> = DV or V <sub>DD</sub>                              |

| lacc   | Quiescent V <sub>CC</sub> Supply Current                        | 18     | -    | 80   | 180  |       | V <sub>IN</sub> = 0V or V <sub>DD</sub>                              |

| lgoo   | Quiescent V <sub>DO</sub> Supply Current                        | 19     | -    | 2.0  | 5.0  | μA    | V <sub>IN</sub> = 0V or V <sub>DD</sub>                              |

| 1114+  | Logic "1" Input Bias Current                                    | 20     | -    | 20   | 40   |       | V <sub>IN</sub> = V <sub>DD</sub>                                    |

| liN-   | Logic "0" Input Bias Current                                    | 21     | -    | -    | 1.0  |       | V <sub>IN</sub> = 0V                                                 |

| VBSUV+ | Vgs Supply Undervoltage Positive Going<br>Threshold             | 22     | 7.4  | 8.5  | 9.6  |       | 43.7.                                                                |

| VBSUV- | V <sub>BS</sub> Supply Undervoltage Negative Going<br>Threshold | 23     | 7.0  | 8.1  | 9.2  | v     |                                                                      |

| Vccuv+ | V <sub>CC</sub> Supply Undervoltage Positive Going<br>Threshold | 24     | 7.6  | 8.6  | 9.6  |       |                                                                      |

| Vocuv- | V <sub>CC</sub> Supply Undervoltage Negative Going<br>Threshold | 25     | 7.2  | 8.2  | 9.2  |       |                                                                      |

| 10+    | Output High Short Circuit Pulsed Current                        | 26     | 200  | 250  | =    |       | V <sub>O</sub> = 0V, V <sub>IN</sub> = V <sub>DD</sub><br>PW ≤ 10 µs |

| lo.    | Output Low Short Circuit Pulsed Current                         | 27     | 420  | 500  | -    | mA    | V <sub>O</sub> = 15V, V <sub>IN</sub> = 0V<br>PW ≤ 10 µs             |

# IR2112(S) & (PbF)

International

IOR Rectifier

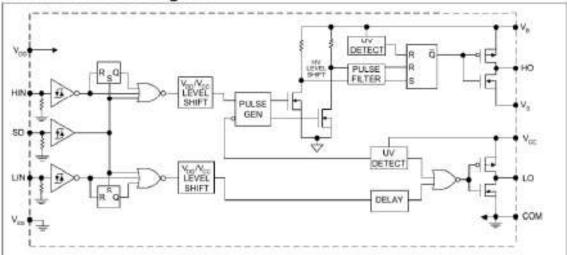

# **Functional Block Diagram**

# **Lead Definitions**

| Symbol         | Description                                                 |  |

|----------------|-------------------------------------------------------------|--|

| VDO            | Logic supply                                                |  |

| HIN            | Logic input for high side gate driver output (HO), in phase |  |

| SD             | Logic input for shutdown                                    |  |

| LIN            | Logic input for low side gate driver output (LO), in phase  |  |

| Vss            | Logic ground                                                |  |

| V <sub>B</sub> | High side floating supply                                   |  |

| HO             | High side gate drive output                                 |  |

| Vs             | High side floating supply return                            |  |

| Vcc            | Low side supply                                             |  |

| LO             | Low side gate drive output                                  |  |

| COM            | Low side return                                             |  |

# Lead Assignments